## FPGA

FIELD PROGRAMMABLE GATE ARRAY

### Arreglo Programables

A los circuitos digitales que son programables en hardware usando lenguajes como VHDL se les conoce como dispositivos lógicos programables (PLDs, Programmable Logic Devices).

- SPLD (Simple Programmable Logic Devices)

- PAL (Programmable Array Logic)

- GAL (Generic Array Logic)

- CPLD (Complex Programmable Logic Devices)

- ✓ FPGA (Field-Programmable Gate Arrays)

# Simple Programmable Logic Devices (SPLD)

- ✓ PAL (Programmable Array Logic). Se programa solo una vez.

- ✓ GAL. (Generic Array Logic). Es un tipo de PAL que es reprogramable.

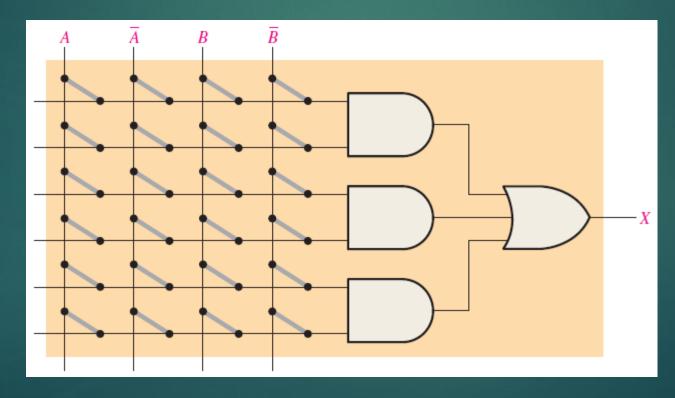

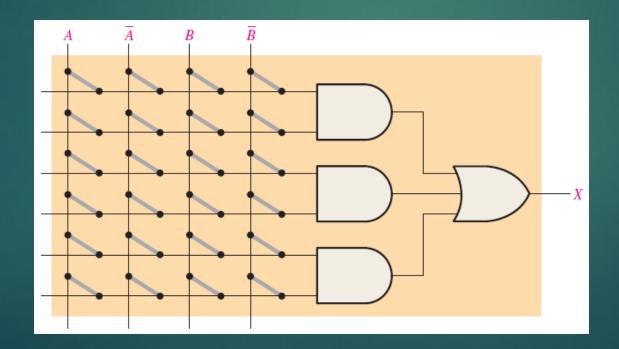

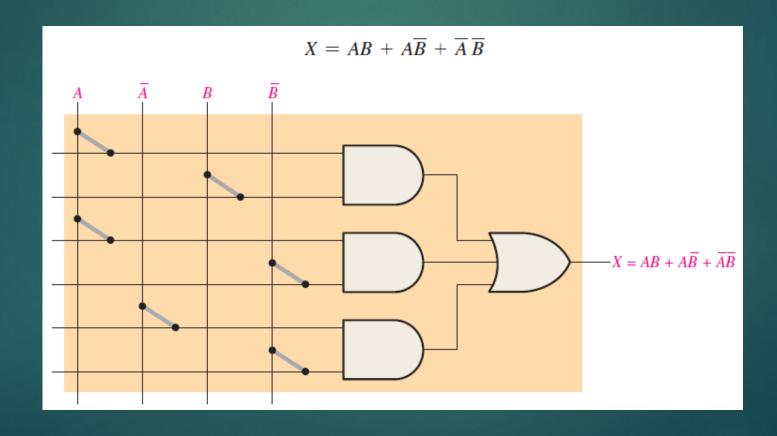

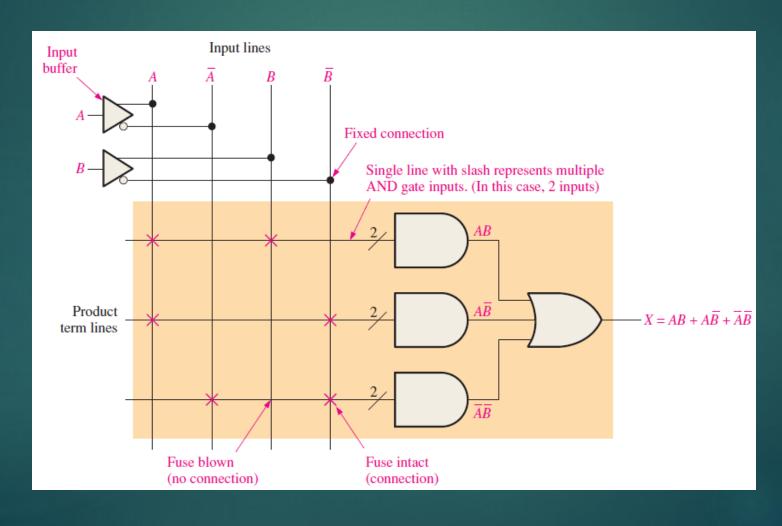

- La estructura básica de ambos dispositivos es un arreglo programable de compuertas AND y un arreglo fijo de compuertas OR. Esto es, una arquitectura de suma de productos.

Arreglo programable de compuertas AND y arreglo fijo de compuertas OR.

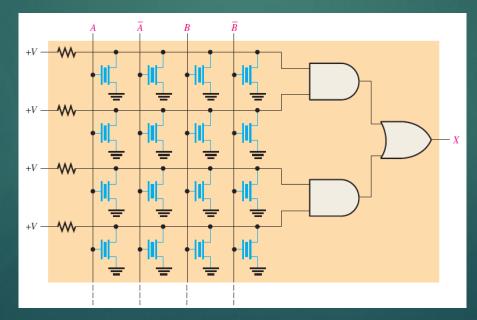

Es esencialmente una matriz o rejilla de conductores que forman filas y columnas con un enlace (unión) programable en cada punto de cruce. Cada unión programable, se llama celda.

- ✓ La arquitectura SOP permite implementar cualquier expresión lógica de suma de productos.

- Programando la presencia o ausencia de una conexión, cualquier combinación deseada de las variables de entrada o sus complementos puede aplicarse al arreglo de compuertas AND para formar un producto deseado.

- ✓ Las compuertas AND se conectan a la compuerta OR.

Ejemplo

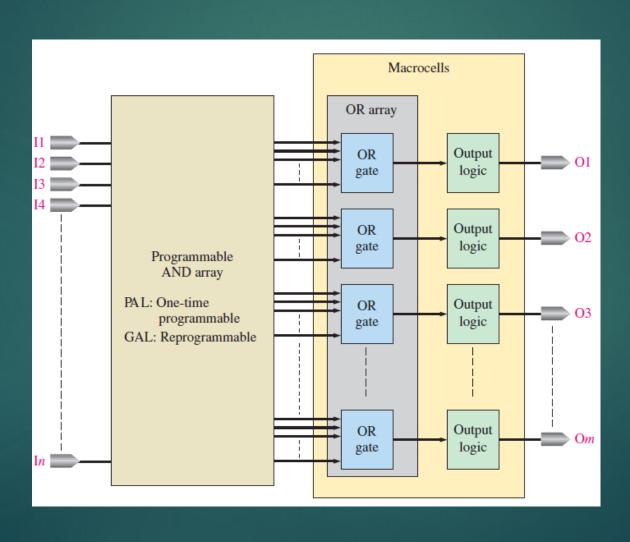

PAL (Programmable Array Logic) y GAL (Generic Array Logic) tienen varias entradas y varias salidas.

La GAL es esencialmente una PAL que puede reprogramarse: usa una tecnología de proceso reprogramable, tal como EEPROM, en lugar de

fusibles.

### SLPD - Logic Array Block (LAB)

#### SPLD – Macro Celdas

- ✓ Consiste de una compuerta OR y alguna lógica de salida.

- Puede configurarse para lógica combinacional, lógica de registro o una combinación de ambos.

- Lógica de registro se refiere que hay un flip-flop para proporcionar funciones lógicas secuenciales.

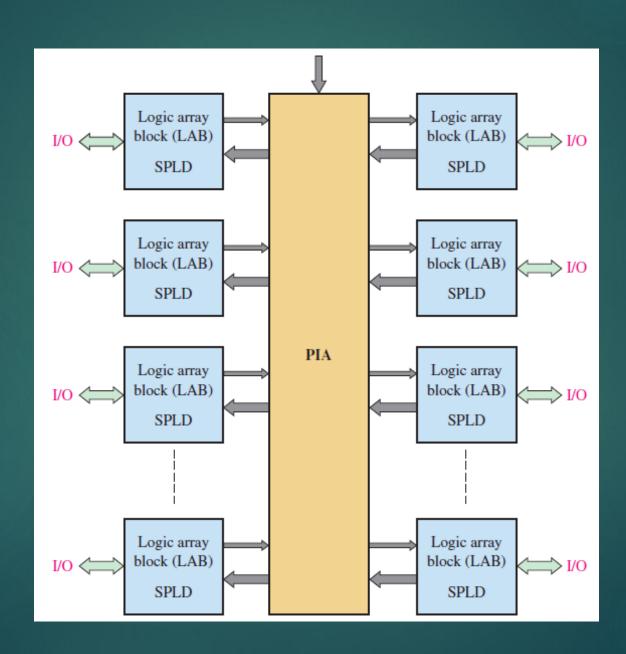

# Complex Programmable Logic Devices (CPLD)

- ✓ Un CPLD es un dispositivo que contiene múltiples SPLDs y proporciona mayor capacidad para diseños más grandes.

- ✓ Los arreglos SPLDs tienen interconexiones programables entre ellos. Cada arreglo SPLD se conoce como LAB (Logic Array Block).

- Las interconexiones entre SPLDs se conocen como PIA (Programmable Interconnect Array) o AIM (Advenced Interconnect Matrix).

- ✓ Los LABs y las interconexiones entre LABs se programan vía software.

### **CPLD**

#### **CPLD**

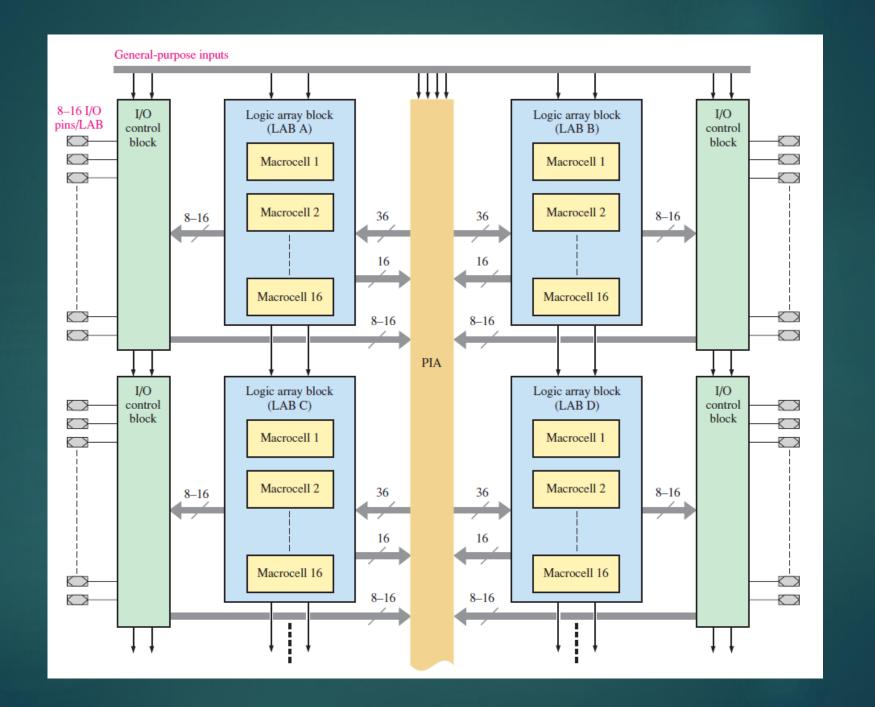

- ✓ La arquitectura de un CPLD consiste en la forma en que los elementos internos están organizados y arreglados.

- ✓ Tiene la estructura de una PAL/GAL que produce funciones SOP.

- Consiste entre 12 y 16 LABs, donde cada LAB consiste de varias macro celdas.

- Los LABs están unidos entre sí a través del PIA, el cual es una estructura de bus programable. El PIA se conectan las entradas, salidas y macro celdas.

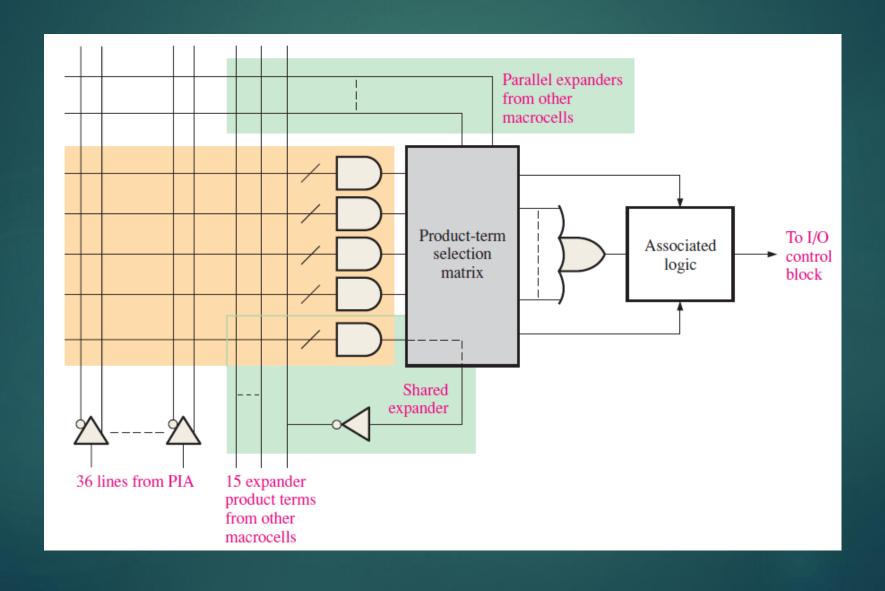

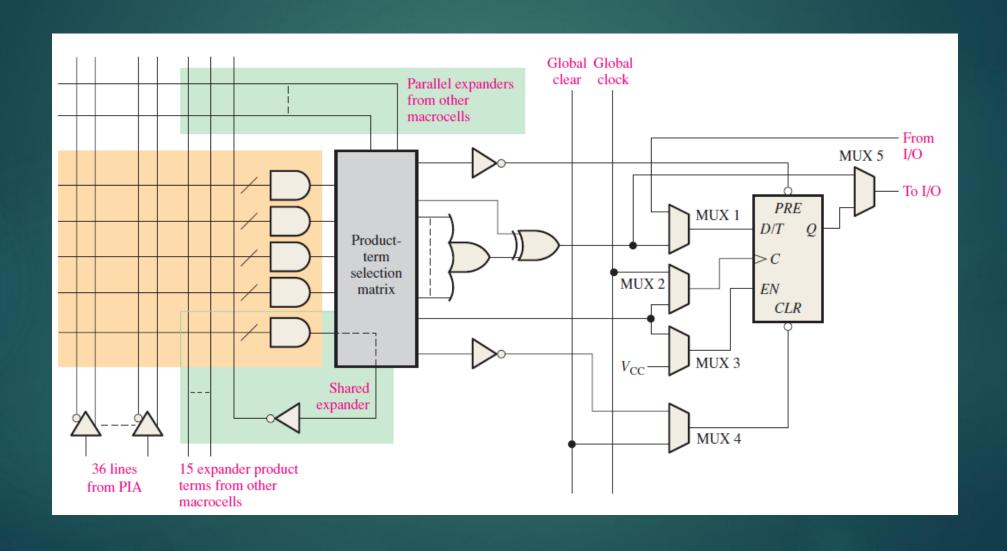

#### CPLD - Macro Celdas

#### Consiste en

- Un arreglo de compuertas AND programables.

- ✓ Una compuerta OR.

- Una matriz de selección de productos para conectar las salidas de las compuertas AND a la compuerta OR.

- Una lógica asociada que puede programarse para entrada, salida de lógica combinacional o salida de registro.

Difiere de la macro celda definida en los SPLDs, pues permite expandir las expresiones SOP.

### CPLD - Macro Celdas

### CPLD - Macro Celdas

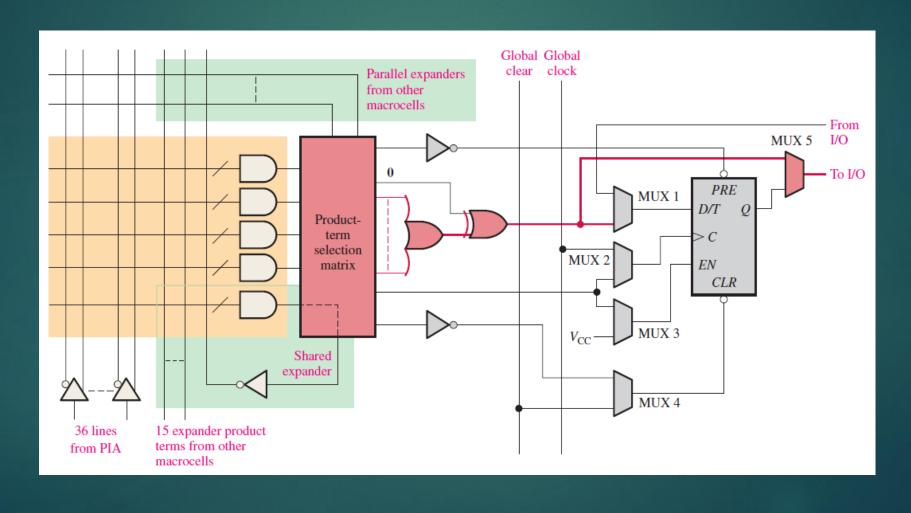

## CPLD – Macro Celdas – Modo Combinacional

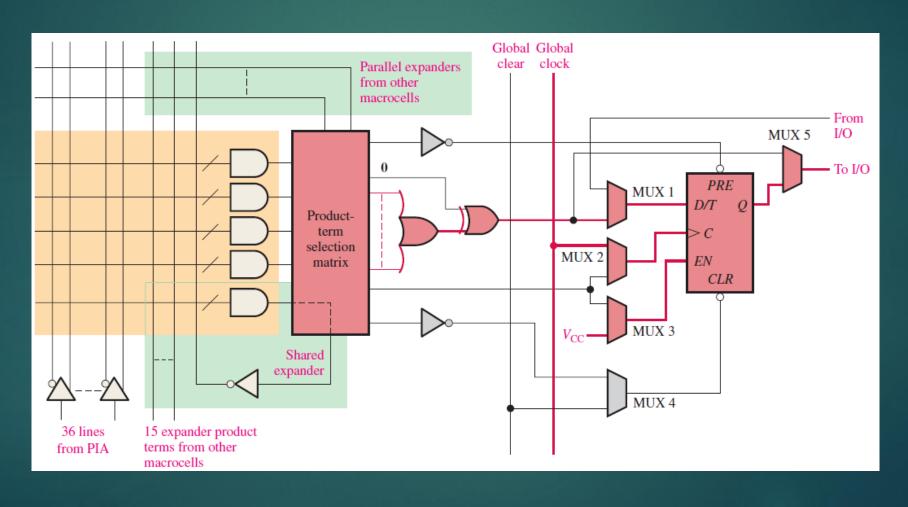

### CPLD – Macro Celdas – Modo Registro

# Field-Programmable Gate Arrays (FPGA)

La arquitectura de un CPLD consiste de bloques PAL/GAL con interconexiones programables. El FPGA difiere en que no usa arreglos tipo PAL/GAL.

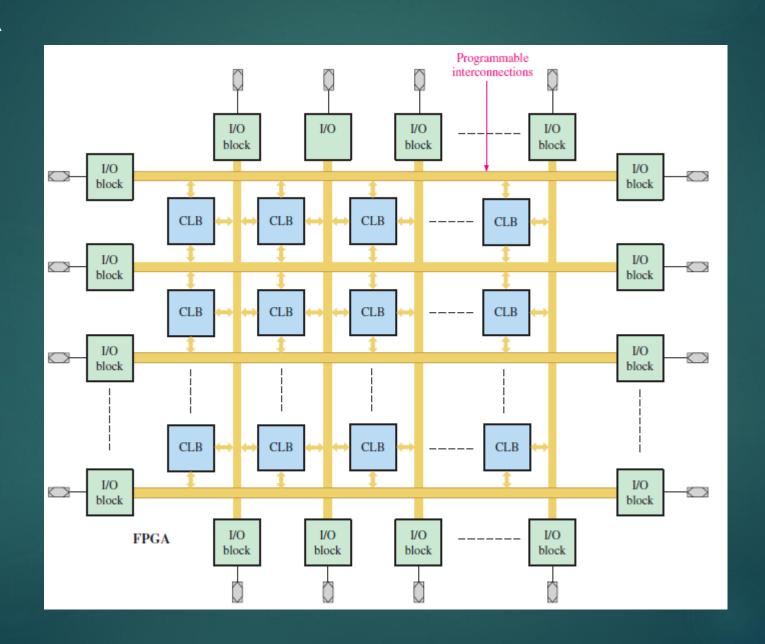

#### Los tres elementos en un FPGA son:

- Bloque Lógico configurable (CLB, Configurable Logic Block)

- ✓ Interconexiones.

- ✓ Bloques de entrada y salida (I/O Blocks)

### **FPGA**

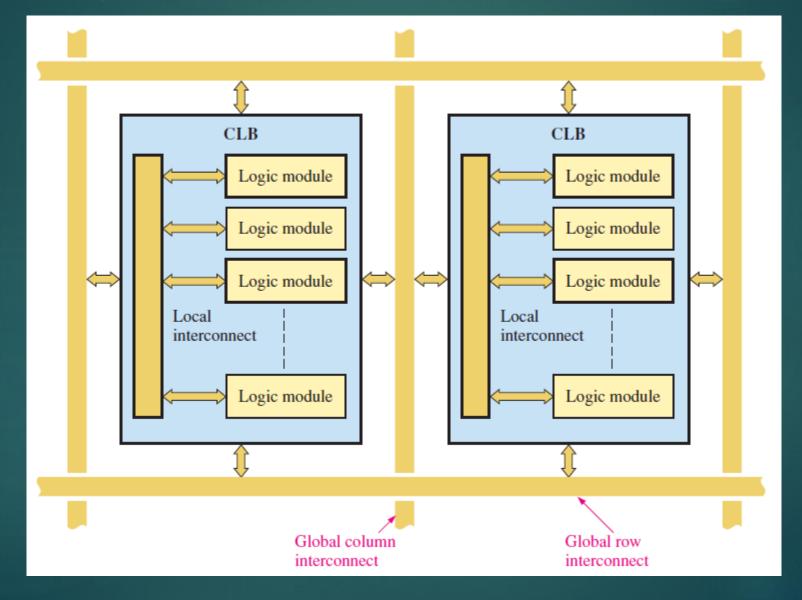

#### FPGA - CLB

- ✓ También se conocen como bloques de arreglo lógico, (LAB, Logic Array Logic).

- Consiste de algunos módulos lógicos pequeños que son las unidades de construcción básica. Son análogos a las macro celdas de un CPLD.

- Cada CLB se construye de múltiples módulos lógicos y un inter conector programable que se usa para conectar los módulos lógicos dentro del CLB.

### FPGA - CLB

#### FPGA – LOGIC MODULE

- ✓ Pude configurarse para hacer lógica combinacional, lógica de registro o ambos.

- Un flipflop es parte de la lógica asociada y se usa para la lógica de registro.

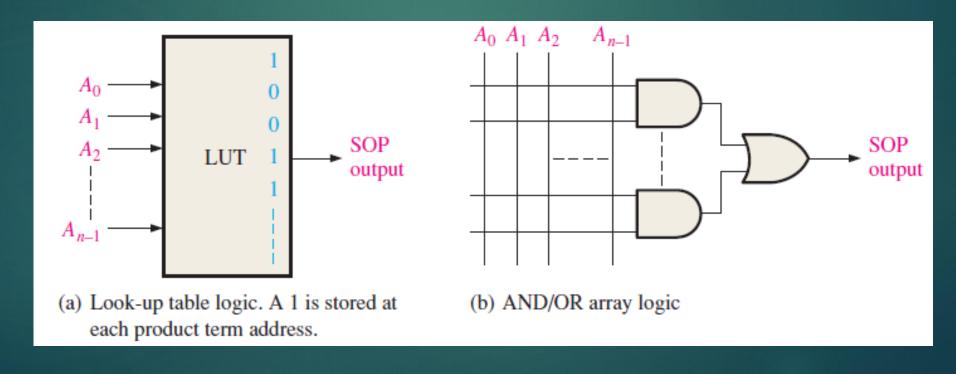

- ✓ El LUT hace esencialmente hace el mismo trabajo que el PAL

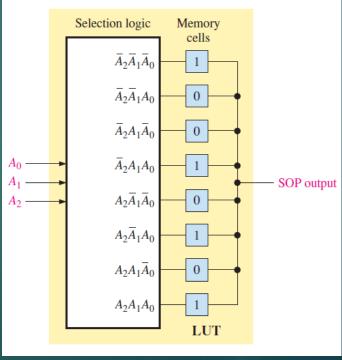

#### FPGA – LOOK-UP TABLES

Una LUT (Look-Up Tables) es un tipo de memoria que puede programarse para producir funciones SOP. Se usan en lugar de los arreglos AND/OR.

#### FPGA – LOOK-UP TABLES

La organización de una LUT consiste de un número de celdas de memoria igual a 2<sup>N</sup>, done N es el número de variables de entrada. Por ejemplo una LUT de 3 entradas puede producir una expresión SOP con hasta 8 términos.

Ejemplo

$$\overline{A}_2\overline{A}_1\overline{A}_0 + \overline{A}_2A_1A_0 + A_2\overline{A}_1A_0 + A_2A_1A_0$$

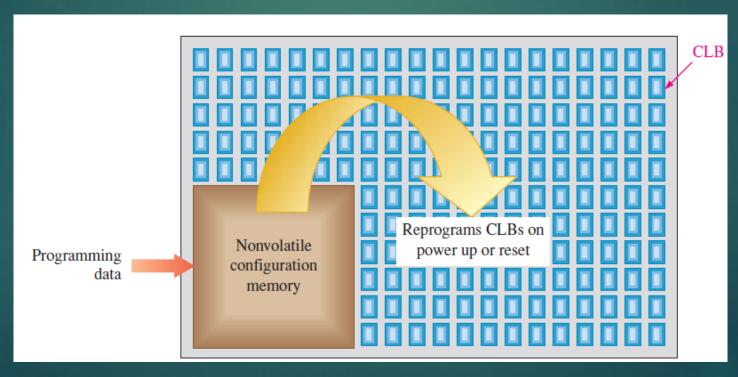

#### FPGA basados en SRAM

Incluyen una memoria no volátil sobre el chip para almacenar la información del programa y reconfigurar al dispositivo cada vez que se energice.

### FPGA - NÚCLEOS

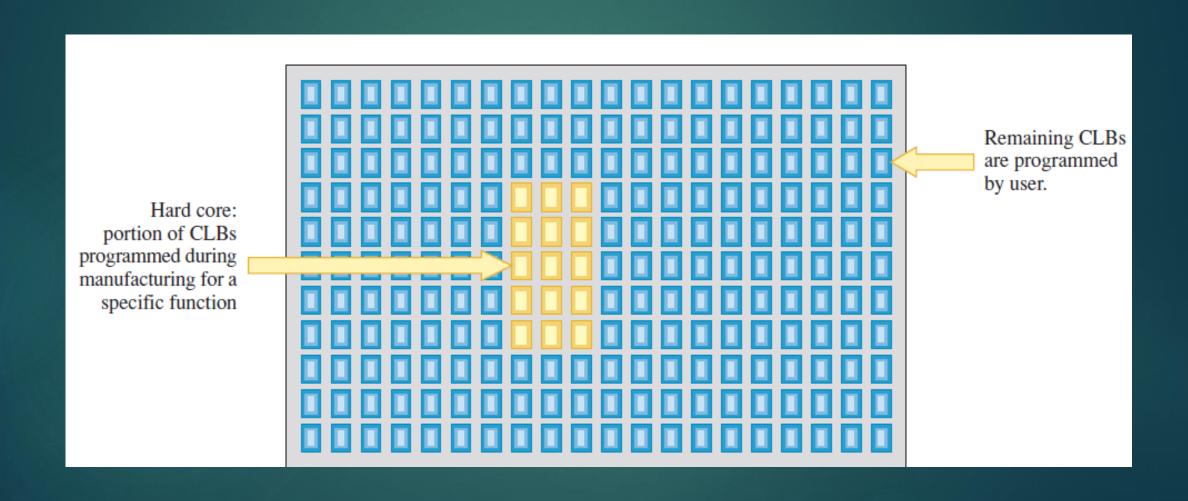

Los FPGAs son esencialmente como tablillas (protoboards) en blanco que el usuario final puede programar para cualquier diseño lógico.

Hay FPGAs que contienen un núcleo lógico duro o suave.

El núcleo lógico duro es una porción de lógica dentro del FPGA que es puesta por el fabricante para proporcionar una función especifica y que no puede reprogramarse.

El núcleo lógico suave se tiene cuando la función embebida tiene algunas características programables.

### FPGA - NÚCLEOS

### FPGA – Parámetros Importantes

| Característica            | Rango                |

|---------------------------|----------------------|

| Número de LEs             | 1,500 - 813,000      |

| Número de CLBs            | 26 - 359,000         |

| Memoria embebida          | 26kb – 63Mb          |

| Número de I/Os            | 18 – 1200            |

| Voltaje de operación (DC) | 1.8V, 2.5V, 3.3V, 5V |

### Fabricantes

| Fabricante | Nombre de la serie                                             | Software de diseño         | Página de internet |

|------------|----------------------------------------------------------------|----------------------------|--------------------|

| Altera     | Stratix<br>Aria<br>Cyclone                                     | Quartus II                 | Altera.com         |

| Xilinx     | Spartan<br>Artix<br>Kintex<br>Virtex                           | ISE Design Suite           | Xilinx.com         |

| Lattice    | iCE40<br>MachX02<br>Lattice ECP3<br>Lattice XP2<br>LatticeGC/M | Lattice Diamod<br>iCEcube2 | Latticesemi.com    |

| Atmel      | AT40                                                           | IDS                        | Atmel.com          |

### Diferencias entre FPGAs y CPLDs

| Características | CPLD                                              | FPGA                                                                                               |

|-----------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Arquitectura    | Utilizan AND y OR.                                | Utilizan LUTs. Incluyen<br>circuitos específicos<br>prediseñados: RAM, DSP.<br>Sistemas embebidos. |

| Tecnología      | Utiliza FLASH                                     | Utiliza RAM                                                                                        |

| Densidad        | Baja a media (1000<br>compuertas<br>equivalentes) | Media alta (millones de<br>compuertas<br>equivalentes)                                             |

| Aplicaciones    | Aceleradores<br>Lógica combinacional              | Excelentes para arquitecturas de computadores, DSP, DIP.                                           |